# ACT 1<sup>™</sup>Family Gate Arrays Product Guide

May 1989

ACT, Action Logic, Activator, Actionprobe and PLICE are trademarks of Actel Corporation. IBM is a registered trademark of International Business Machines Corporation. Viewlogic is a registered trademark of Viewlogic Systems, Incorporated. Actel Corporation reserves the right to make changes to any products or services herein at any time without notice. Actel does not assume any responsibility or liability arising out of the application or use of any product or service described except as expressly agreed to in writing by Actel.

©1988 Actel Corporation.

Actel Corporation 955 East Arques Avenue Sunnyvale, CA 94086-4520 (408) 739-1010

# **Data Sheets:**

Action Logic System ACT1 Family Gate Arrays Actel Library

# **Application Notes:**

Gate Array Design UART Design

# **Applications Briefs:**

Three-Stating ACT 1010/1020 Designs ALU181 Fast Adders 8-bit Twos Complement Multiplier The Actel Timer Using the Actionprobes Metastability

•

# **Data Sheets:**

Action Logic System ACT1 Family Gate Arrays Actel Library

# Action Logic<sup>TM</sup> System

# Features:

- Extensive Gate Array Macro Library

- Supports Popular CAE systems

- Design Validation, Electrical Rules Check

- Fully Automated Place and Route

- Menu-driven Pin Editor for I/O Assignment

- Timing Analyzer Inspects all Critical Paths and AC Specifications

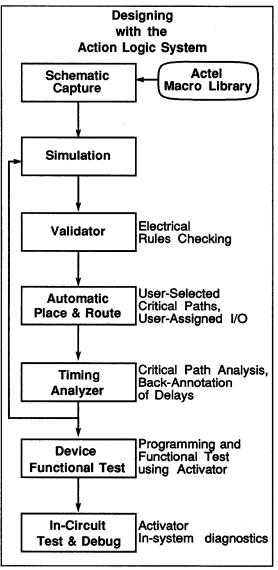

# **Designing with the Action Logic System**

#### Overview

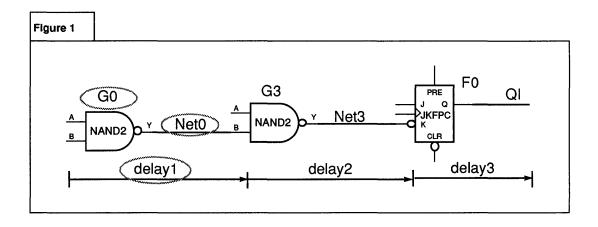

The Action Logic System is a high-productivity CAE environment for implementing logic functions with ACT devices. A menu-driven interface allows users to complete ACT™1 gate array designs, from concept to silicon, within hours without costly NRE. The system includes a software design environment and an Activator programmer, tester and debugger. Most popular CAE platforms are supported. Designers use their workstation to capture schematics, simulate, verify, place & route, perform timing analysis, program, and debug the chip at their desk. Actel's on-line help screens and reference manuals speed and simplify the design process.

#### **Gate Array Macro Library**

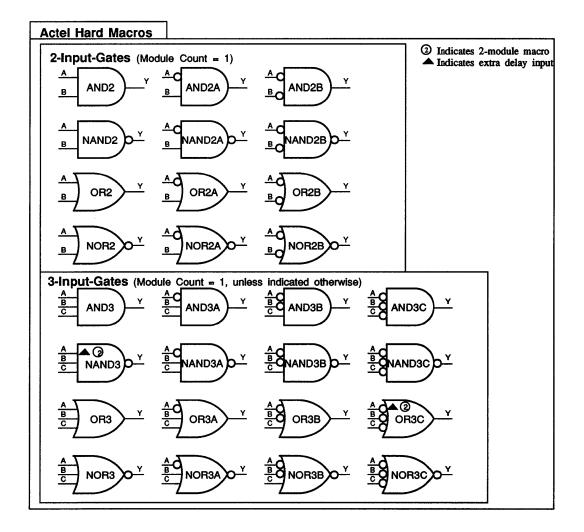

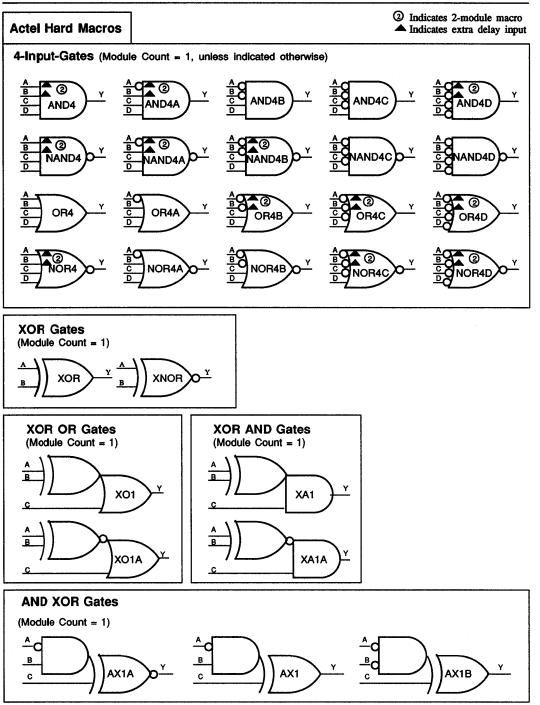

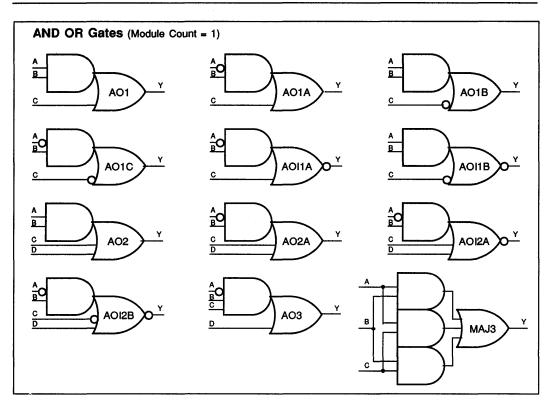

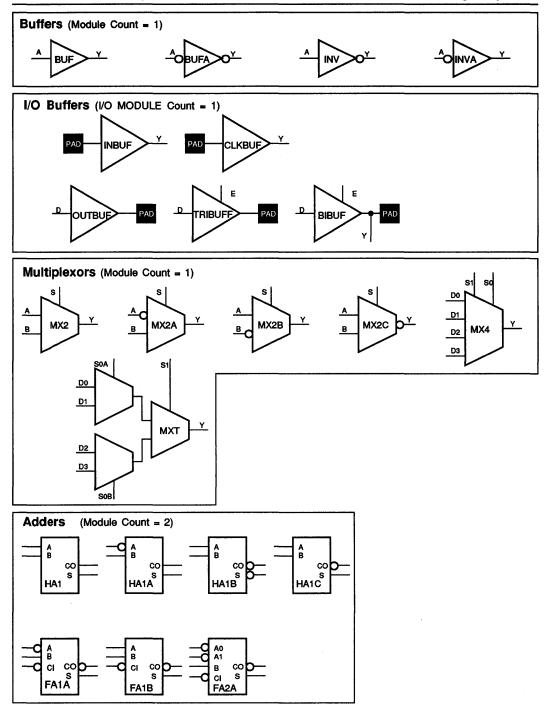

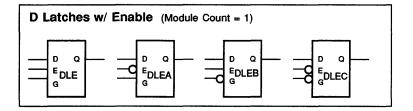

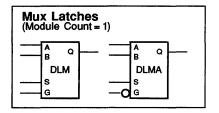

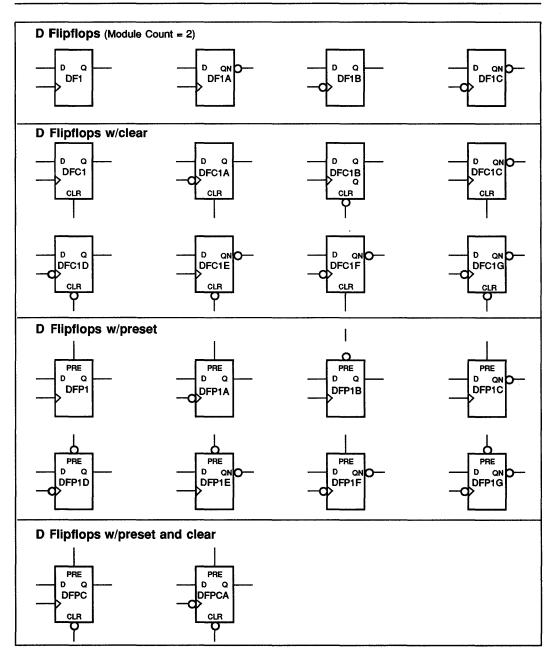

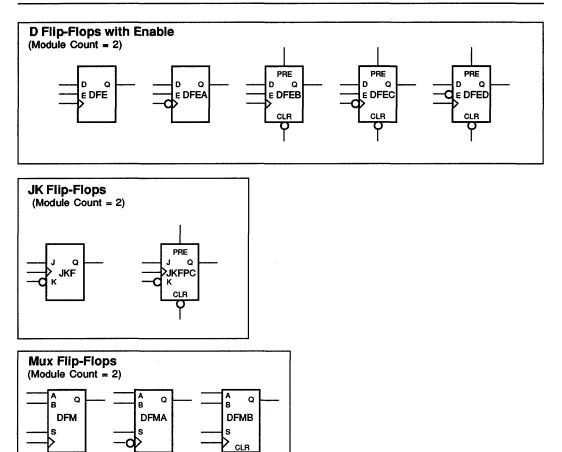

The Actel macro library contains the logic function building blocks necessary to create a design. The library includes macros ranging in complexity from simple gates to complex functions. Each macro has a graphic symbol or icon. Hard macros also contain placement information, a netlist and timing data.

Basic gates from the library are used to create soft macros like counters, adders and decoders. The Actel library contains over 150 different macros.

#### Schematic Capture and Simulation

Users enter their schematic using the Actel library. When completed, functional simulation is performed on the design.

#### **Pin Editor**

The Actel Pin Editor is an easy-to-use, menu-driven program for user assignment of logic I/Os and package pins. The editor automatically scrolls a list of all user-designated I/Os. To assign any pin to an I/O, the user enters the desired pin number next to the I/O node name. During each pin assignment, the Editor insures each pin is a valid package pin and is not already assigned to another chip I/O.

# **Design Validation**

The Actel Design Validator examines an ACT design for adherence to design rules specific to the ACT device chosen for the design. Validation verifies routability, and performs design rules checks prior to routing. The Validator produces error and information messages, and svstem warnings regarding electrical rules violations such as excessive fanout, shorted outputs, or unconnected inputs. A warning is issued, for example, if a net exceeds a fanout of ten; unconnected module inputs produce an error message.

The Validator also provides statistical information about routability, logic module count, I/O count, average fanout per net, and array utilization. After passing design through the, the design is free of electrical rules violations.

## Automatic Place & Route

Fully automatic place and route software minimizes design delay by assigning macros to optimal locations in the chip. The system uses the design's netlist, critical net information and I/O assignments to automatically place and route all the logic blocks within the circuit.

The software provides the user with data on actual wire length, capacitive loading and wiring congestion. The route program assigns the shortest possible net segments to connect the library macros with minimal delay, routing 100% of the nets automatically for 85-95% logic module utilization. The program provides data on actual wire length, capacitive loading and wiring congestion. No manual intervention is required, even at high device utilization.

Actel Place and Route takes advantage of The ACT device's efficient architecture and abundance of routing resources to consistently place and route 100% of the nets.

## **Timing Analysis**

The timing analyzer is an interactive tool which determines and highlights all critical and non-critical paths within a specified design. After the layout phase is complete, the Timing Analyzer extracts accurate net delays. These delays are backannotated to the netlist and evaluated with the timing analyzer or simulator. It provides data concerning the slowest paths in the design and any other user specified paths. Using this information, the designer optimizes the design to meet its timing specifications. The Timer accepts as its input the design's netlist and delay information. The user directs the type of analysis and output. Delay reports generated by the Timing Analyzer using numbers provide the final AC post-route specifications for the designs.

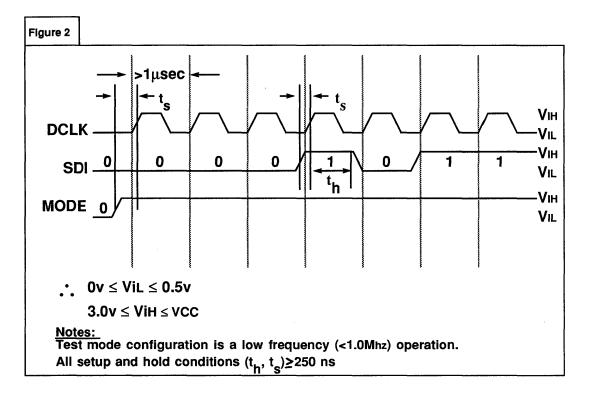

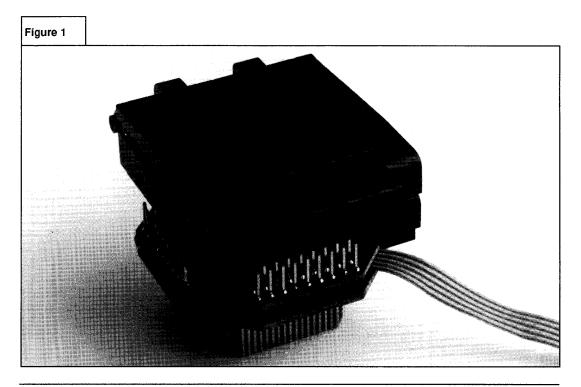

#### **Device Programming**

Programming is controlled by the Activator™ programming system. Action Logic software generates a fuse map for the ACT device which is used by the Activator for programming. A series of internal address registers are automatically loaded specifying the programming element (PLICE antifuse) to be programmed. A programming sequence is then initiated, creating a permanent link. These steps are repeated until all interconnections are made.

## **Functional Test**

The Activator supports functional testing using an I/O test vector file. It also supports interactive circuit debugging.

#### In-circuit Test and Debug

Once the device is programmed and functionally verified, it is ready for operation in the user's system. The Actionprobe diagnostics may then be used to further evaluate circuit integrity.

# ACT<sup>™</sup>1 Family Desktop Configurable Gate Arrays

## Features:

- High Gate and I/O Count: ACT1010-- 1200 gates, 57 I/Os ACT1020-- 2000 gates, 69 I/Os

- Instant Prototypes and Production

- Toggle rates to 70 MHz

- System-Level Performance to 40 MHz

- Gate Array Architecture Allows Completely Automatic Place and Route

- Non-Volatile, Permanent Programming

- Built-In Clock Distribution Network

- Built-In Diagnostic Probes

- Low Power CMOS technology

- Fully supported by Actel's Action Logic™ System

# ACT1010/1020 Description

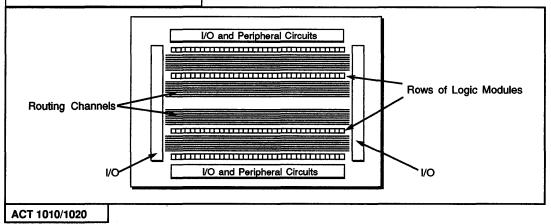

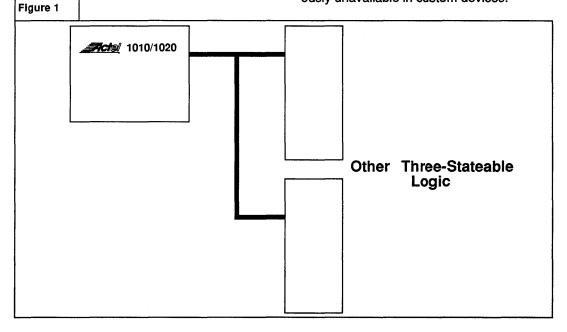

Figure 1: ACT Device Architecture

ACT1010 and ACT1020 devices are the first members of a family of Application Configurable Technology (ACT) gate arrays offered by Actel. These devices are implemented in silicon gate, 2 micron, 2level metal CMOS, employing Actel's PLICE™ antifuse technology. The unique architecture offers gate array flexibility, high performance and instant turnaround through user programming. Utilizations as high as 90% permit designs of 1200 equivalent gates for the ACT1010, and 2000 gates for the ACT1020.

The ACT1010/1020 also provide system designers with unique on-chip diagnostic probe capabilities allowing convenient testing and debugging. Additional features include an on-chip clock driver with a hard wired distribution network. The network provides efficient clock distribution with minimum skew.

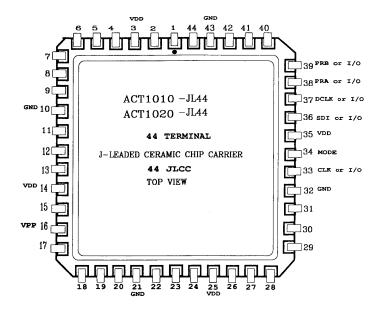

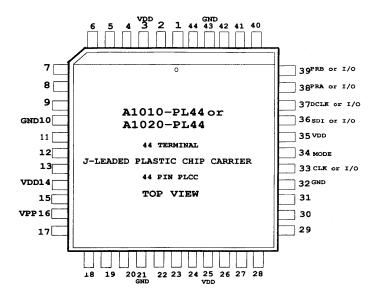

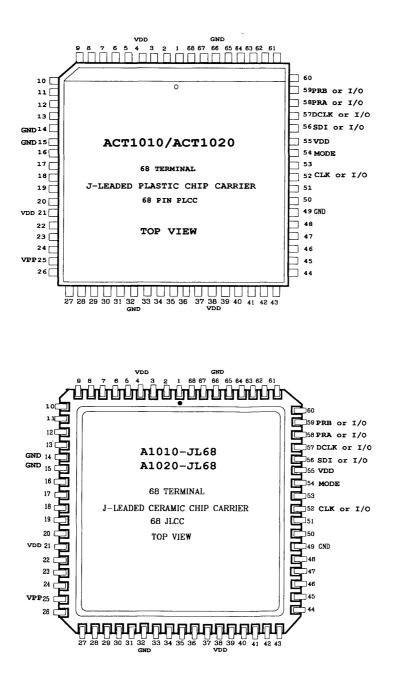

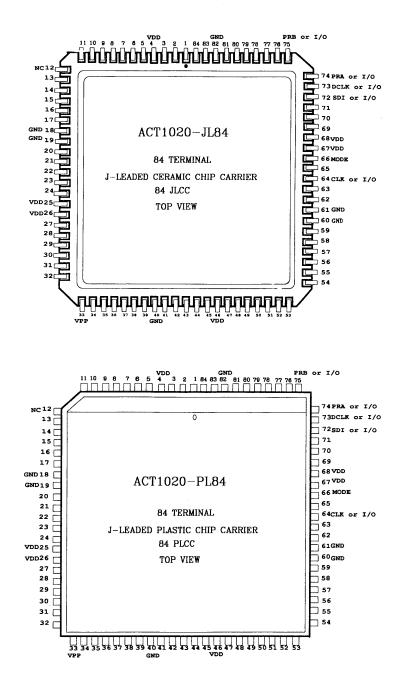

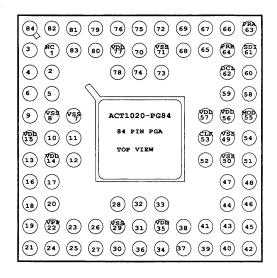

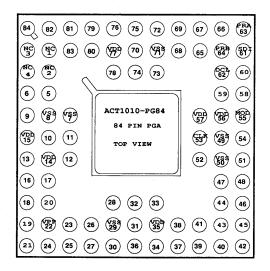

The user-configurable I/Os are capable of driving at both TTL and CMOS drive levels. The ACT1010/1020 are available in 44, 68 and 84 pin leaded chip carriers, and 84PGA.

The ACT device signature register offers programmable identification for both part type and user ID information. A security fuse may be used to permanently disable all further programming, diagnostics and testing once the chip is configured. Designs are thus protected from copying or reverse engineering.

# Action Logic System Description

ACT1010/1020 devices are supported by Actel's Action Logic System, providing logic design implementation with minimum effort. The Action Logic System interfaces with the resident CAE system to provide a complete gate array design environment: schematic capture, simulation, fully automatic place and route, timing verification and device programming. The Action Logic System is available for 386 PC and compatible workstations, including Apollo and Sun workstations.

Actel Corporation, 955 East Arques Avenue, Sunnyvale, CA 94086-4520 (408) 739-1010

# ACT 1 Desktop Configurable Gate Arrays

# **ACT Device Structure**

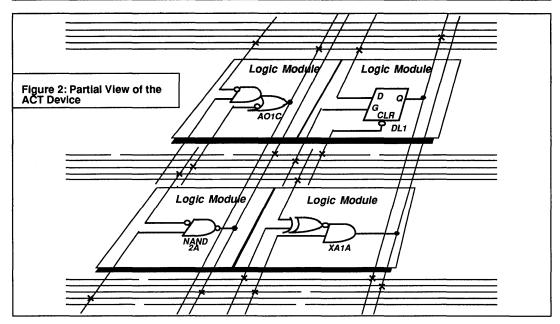

A partial view of an ACT device (Figure 2) shows four logic modules and distributed horizontal and vertical interconnect tracks. Logic module inputs, outputs, and track segments are connected via PLICE antifuses located at intersections. During programming, these antifuses are addressed and programmed to make the connections required by the circuit application.

## The Actel Logic Module

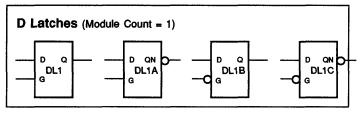

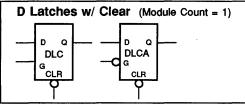

The Actel logic module is an eight input, one output configurable logic circuit chosen for the wide range of functions it implements and for its efficient use of interconnect routing resources.

The logic module can implement the four basic logic functions (NAND, AND, OR, and NOR) in gates of two, three or four inputs. Each function may have many versions, with different combinations of active-low inputs. The logic module can also implement a variety of D-latches, exclusivity function, AND-ORs, and OR-ANDs. No dedicated hardwired latches or flip-flops are required in the array since latches and flip-flops may be constructed from logic modules wherever needed in the application.

## I/O Buffers

Each I/O pin is configurable as an input, output, three-state, or bi-directional buffer. Input and out-

put levels are compatible with standard TTL and CMOS specifications. Outputs sink or source 4 mA at TTL levels. See the DC Characteristics for additional I/O buffer specifications.

## **Device Organization**

ACT devices consist of a matrix of logic modules arranged in rows separated by wiring channels (Figure 1). This array is surrounded by a ring of peripheral circuits including I/O buffers, testability circuits, and diagnostic probe circuits providing real-time diagnostic capability. Between rows of logic modules are routing channels containing sets of segmented metal tracks with PLICE antifuses. Each channel has 22 signal tracks. The resulting network allows arbitrary and flexible interconnections between logic modules and to I/O modules.

## **Actionprobe Diagnostics**

ACT1010/1020 devices each have two independent diagnostic probe pins. These pins allow the user to observe any two internal signals by entering the appropriate net name in the diagnostic software. Signals may be viewed on an oscilloscope, logic analyzer or with the Action Logic System. The probe pins can also be used as userdefined I/Os, according to the level of the mode control pin. When configured as user-defined I/Os, the pins have the same characteristics as other I/O pins.

#### **ACT Array Performance**

#### Worst-Case Delay Conversion

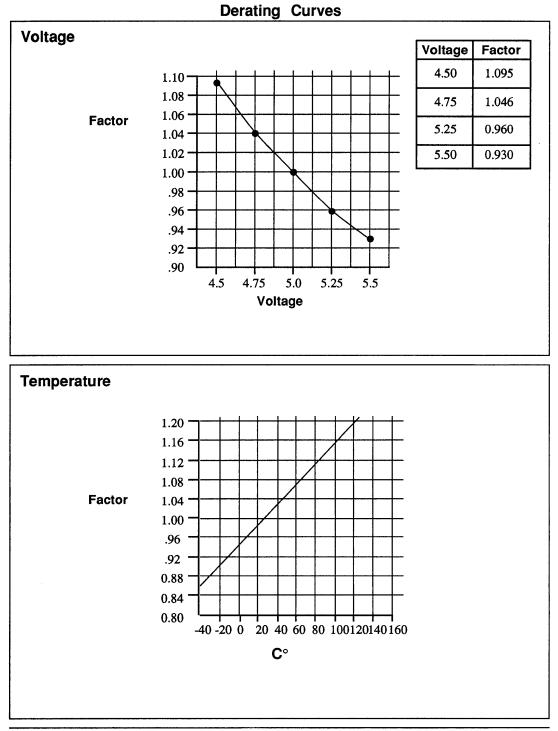

Worst-case delays for ACT arrays are calculated in the same manner as for masked array products. Typical delay parameters are multiplied by factors to account for temperature and voltage effects. However, in an ACT array, temperature and voltage effects are less dramatic than with masked devices. This is due to the fact that the electrical characteristics of module interconnections on ACT devices remain constant over voltage and temperature fluctuations. Therefore, unlike masked devices, performance variations of ACT arrays from voltage and temperature changes are due only to changes in the active devices.

As a result, the total derating factor from typical to worst case for an ACT array is only 1.18 to 1, compared to 2 to 1 for a masked gate array.

#### Logic Module Size

Logic module size also affects performance. A mask programmed gate array cell with four transistors usually implements only one logic level. In an ACT array's more complex logic module (similar to the complexity of a gate array macro), implementation of multiple logic levels within a single module is possible. This eliminates interlevel wiring and associated RC delays. The effect is termed "net compression."

#### **Derating Curves**

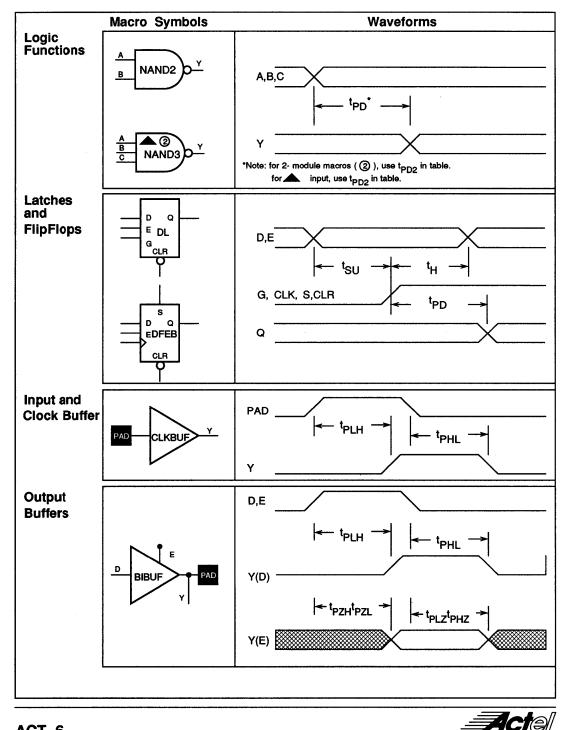

Logic module and storage element delays are shown in the tables on page 5. These delays may be used directly from the table for estimating purposes. Temperature and voltage are derated according to the curves in the graphs on page 7. The Action Logic System timing analyzer provides actual timing specifications for each circuit implementation.

| Resources                                                                                                                                                       |                                                                                                                                        |                                                                                                                                                                                                                             |                                 | ACT                                                                                                         | 010                                                                                                            | ACT                                                                 | 020                                                    |                             |                                                     |                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|-----------------------------|-----------------------------------------------------|---------------------------------------------|

|                                                                                                                                                                 |                                                                                                                                        | Logic Modul                                                                                                                                                                                                                 | es                              | 29                                                                                                          | 295 54                                                                                                         |                                                                     | 6                                                      |                             |                                                     |                                             |

|                                                                                                                                                                 |                                                                                                                                        | User Define                                                                                                                                                                                                                 | d I/O                           | 57                                                                                                          | ,*                                                                                                             | 69                                                                  | *                                                      |                             |                                                     |                                             |

| Operating                                                                                                                                                       | Charact                                                                                                                                | eristics                                                                                                                                                                                                                    |                                 |                                                                                                             |                                                                                                                |                                                                     | *Incl                                                  | udes                        | diagno                                              | stic pins                                   |

|                                                                                                                                                                 |                                                                                                                                        | solute Maxim                                                                                                                                                                                                                | num R                           | atings*                                                                                                     | 7                                                                                                              |                                                                     |                                                        |                             |                                                     |                                             |

|                                                                                                                                                                 | Pa                                                                                                                                     | rameter                                                                                                                                                                                                                     | Syn                             | nbol L                                                                                                      | imits.                                                                                                         |                                                                     | U                                                      | <u>nitş</u>                 |                                                     |                                             |

|                                                                                                                                                                 |                                                                                                                                        | C Supply Voltage<br>out Level                                                                                                                                                                                               | vo<br>V <sub>I</sub>            |                                                                                                             | 0.3 to +7<br>0.3 to V0                                                                                         |                                                                     |                                                        | olts<br>olts                |                                                     |                                             |

|                                                                                                                                                                 | Sto                                                                                                                                    | orage Temp Rang                                                                                                                                                                                                             | ge T <sub>S</sub>               | STG <sup>-</sup> '                                                                                          | 40 to +1                                                                                                       | 25                                                                  | °C                                                     | ;                           |                                                     |                                             |

| under "recomme<br>periods may affe                                                                                                                              | ect device r                                                                                                                           | anctional operation<br>rating conditions" is<br>reliability.                                                                                                                                                                |                                 |                                                                                                             |                                                                                                                |                                                                     | naximu                                                 | m-rate                      | d conditio                                          | ons for ext                                 |

|                                                                                                                                                                 | Pa                                                                                                                                     | rameter                                                                                                                                                                                                                     | Svn                             | nbol L                                                                                                      | imits                                                                                                          | <br>U                                                               | nits                                                   |                             |                                                     |                                             |

|                                                                                                                                                                 |                                                                                                                                        | Supply Voltage                                                                                                                                                                                                              | VCC                             |                                                                                                             | .75 to 5.                                                                                                      | -                                                                   | olts                                                   |                             |                                                     |                                             |

|                                                                                                                                                                 |                                                                                                                                        |                                                                                                                                                                                                                             |                                 | . 4                                                                                                         | ./ວຎວ.                                                                                                         | . <u>2</u> .0 V                                                     |                                                        |                             |                                                     |                                             |

|                                                                                                                                                                 |                                                                                                                                        | ogram Voltage                                                                                                                                                                                                               | VPF                             |                                                                                                             | .75 10 5.<br>'CC*                                                                                              |                                                                     | olts                                                   |                             |                                                     |                                             |

|                                                                                                                                                                 | Pro                                                                                                                                    |                                                                                                                                                                                                                             |                                 | ° V                                                                                                         |                                                                                                                |                                                                     | olts                                                   |                             |                                                     |                                             |

|                                                                                                                                                                 | Pro<br>Op                                                                                                                              | ogram Voltage                                                                                                                                                                                                               | VPF<br><sup>T</sup> A           | > V<br>0                                                                                                    | CC*                                                                                                            | V                                                                   | olts                                                   |                             |                                                     |                                             |

| DC Op                                                                                                                                                           | Pro<br>Op<br>*Exc                                                                                                                      | ogram Voltage<br>erating Ambient                                                                                                                                                                                            | VPF<br><sup>T</sup> A<br>rammin | > V<br>0                                                                                                    | CC*                                                                                                            | V<br>•(                                                             | olts<br>C                                              | %, TA                       | =0°C to                                             | 5 70°C                                      |

| Symbol                                                                                                                                                          | Pro<br>Op<br>*Exc<br>erating                                                                                                           | ogram Voltage<br>erating Ambient<br>cept during prog                                                                                                                                                                        | VPF<br><sup>T</sup> A<br>rammin | P V<br>O<br>Ng                                                                                              | CC*                                                                                                            | V<br>or<br>VCC=                                                     | olts<br>C                                              |                             | =0°C to<br>Max                                      | o 70°C<br>Unit                              |

| Symbol<br><sup>V</sup> IH                                                                                                                                       | Pro<br>Op<br>*Exc<br>erating<br>Par<br>HIGH lev                                                                                        | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristi<br>rameter<br>rel input                                                                                                                               | VPF<br><sup>T</sup> A<br>rammin | > V<br>0<br>19<br><br>Co<br>TT                                                                              | CC*<br>to 70<br>ondition                                                                                       | V<br>or<br>VCC=                                                     | olts<br>C<br>5V±5°<br>Mi<br>2.0                        | n<br>10                     |                                                     | Unit<br>V                                   |

| Symbol<br>V <sub>IH</sub><br>VIL                                                                                                                                | Pro<br>Op<br>*Exc<br>erating<br>Par<br>HIGH lev<br>LOW leve                                                                            | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>rameter<br>rel input<br>el input                                                                                                                  | VPF<br><sup>T</sup> A<br>rammin | > V<br>0<br>19<br>Сс<br>11<br>11                                                                            | CC*<br>to 70<br>Dindition                                                                                      | V<br>°(<br>VCC= {                                                   | olts<br>C<br>5V±5°<br>Mi<br>2.0                        | n<br>10<br>0                |                                                     | Unit<br>V<br>V                              |

| Symbol<br>V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>OH</sub>                                                                                                 | Pro<br>Op<br>*Exc<br>erating<br>Par<br>HIGH lev<br>HIGH lev                                                                            | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>rameter<br>rel input<br>el input<br>el output (Note 1)                                                                                            | VPF<br><sup>T</sup> A<br>rammin | > V<br>0<br>19<br>Сс<br>11<br>11<br>10                                                                      | CC*<br>to 70<br>Dindition<br>L inputs<br>L inputs<br>1 = -4mA                                                  | V<br>vcc= 4<br>is<br>Dc                                             | olts<br>C<br>5V±5°<br>Mi<br>2.0                        | n<br>10<br>0                | Max                                                 | Unit<br>V<br>V<br>V                         |

| Symbol<br>VIH<br>VIL<br>VOH<br>VOH                                                                                                                              | Pro<br>Op<br>*Exc<br>erating<br>HIGH lev<br>LOW leve<br>LOW leve                                                                       | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>rameter<br>rel input<br>el input<br>el output (Note 1)<br>el output (Note 1)                                                                      | VPF<br><sup>T</sup> A<br>rammin | р<br>уд<br>Сс<br>П<br>П<br>П<br>П<br>І<br>Он                                                                | CC*<br>to 70<br>Dindition<br>L inputs<br>L inputs<br>H - 4mA<br>L - 4mA                                        | V<br>VCC= 1<br>IS<br>DC<br>DC                                       | olts<br>C<br>5V±5<<br>Mi<br>2.(<br>0.<br>3.            | n<br>10<br>0<br>7           | Max                                                 | Unit<br>V<br>V                              |

| Symbol<br>V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>OH</sub>                                                                                                 | Pro<br>Op<br>*Exc<br>erating<br>HIGH lev<br>LOW leve<br>HIGH lev<br>LOW leve<br>Input lease                                            | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>rameter<br>rel input<br>el output<br>el output (Note 1)<br>el output (Note 1)<br>cage                                                             | VPF<br><sup>T</sup> A<br>rammin | 2 V<br>0<br>19<br>Cα<br>10<br>10<br>VI-V                                                                    | CC*<br>to 70<br>Dindition<br>Linputs<br>Linputs<br>                                                            | VCC= 1<br>NS<br>DC<br>DC<br>GND                                     | olts<br>C<br>5V±5¢<br>Mi<br>2.0<br>0.<br>3.<br>-1      | n<br>10<br>0<br>7<br>0      | Max<br>0.8<br>0.45<br>10                            | Unit                                        |

| Symbol<br>VIH<br>VIL<br>VOH<br>VOH<br>IN<br>IOZ                                                                                                                 | Pro<br>Op<br>*Exc<br>erating<br>HIGH lev<br>LOW leve<br>HIGH lev<br>LOW leve<br>Input leak<br>3-state o                                | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>rameter<br>rel input<br>el input<br>el output (Note 1)<br>el output (Note 1)<br>cage<br>utput leakage                                             | VPF<br><sup>T</sup> A<br>rammin | 2 V<br>0<br>1g<br>Cα<br>ΤΤ<br>ΤΤ<br>Ιοι<br>V <sub>I</sub> -V                                                | CC <sup>+</sup><br>to 70<br>Dondition<br>L inputs<br>L inputs<br>H - 4mA<br>L - 4mA<br>L - 4mA<br>VCC or 0     | VCC- (<br>IS<br>DC<br>DC<br>GND                                     | olts<br>C<br>5V±5<<br>Mi<br>2.(<br>0.<br>3.            | n<br>10<br>0<br>7<br>0      | Max<br>0.8<br>0.45                                  | Unit<br>V<br>V<br>V                         |

| Symbol<br>V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>OH</sub><br>V <sub>OL</sub><br>IN                                                                        | Pro<br>Op<br>*Exc<br>erating<br>HIGH lev<br>LOW leve<br>HIGH lev<br>LOW leve<br>Input leak<br>3-state o                                | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>rameter<br>rel input<br>el output<br>el output (Note 1)<br>el output (Note 1)<br>cage                                                             | VPF<br><sup>T</sup> A<br>rammin | 2 V<br>0<br>19<br>Cα<br>10<br>10<br>VI-V                                                                    | CC <sup>+</sup><br>to 70<br>Dondition<br>L inputs<br>L inputs<br>H - 4mA<br>L - 4mA<br>L - 4mA<br>VCC or 0     | VCC- (<br>IS<br>DC<br>DC<br>GND                                     | olts<br>C<br>5V±5¢<br>Mi<br>2.0<br>0.<br>3.<br>-1      | n<br>10<br>0<br>7<br>0      | Max<br>0.8<br>0.45<br>10                            | Unit                                        |

| Symbol<br>VIH<br>VIL<br>VOH<br>VOL<br>IN<br>IOZ                                                                                                                 | Pro<br>Op<br>*Exc<br>erating<br>HIGH lev<br>LOW leve<br>HIGH lev<br>LOW leve<br>Input leak<br>3-state o<br>VCC sup                     | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>rameter<br>rel input<br>el input<br>el output (Note 1)<br>el output (Note 1)<br>cage<br>utput leakage                                             | VPF<br><sup>T</sup> A<br>rammin | 2 V<br>0<br>1g<br>Cα<br>Cα<br>Π<br>Π<br>1ο<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V | CC*<br>to 70<br>Dindition<br>Linputs<br>Linputs<br>- 4mA<br>- 4mA<br>/CC or 0<br>VCC or<br>or GND,<br>/0 = VC0 | VCC= 1<br>IS<br>DC<br>DC<br>GND<br>GND<br>I <sub>0</sub> = 0mA<br>C | olts<br>C<br>5V±5<br>0.<br>0.<br>3.<br>-1<br>-1<br>-1  | n<br>00<br>7<br>0<br>0<br>0 | Max<br>0.8<br>0.45<br>10<br>10<br>10<br>140         | Unit<br>V<br>V<br>V<br>µA<br>µA<br>mA<br>mA |

| Symbol<br>VIH<br>VIL<br>VOH<br>VOH<br>IN<br>IOZ<br>IDD1                                                                                                         | Pro<br>Op<br>*Exc<br>erating<br>HIGH lev<br>LOW leve<br>HIGH lev<br>LOW leve<br>Input leak<br>3-state o<br>VCC sup                     | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>ameter<br>rel input<br>el output<br>el output (Note 1)<br>el output (Note 1)<br>cage<br>utput leakage<br>oply (standby)                           | VPF<br><sup>T</sup> A<br>rammin | 2 V<br>0<br>1g<br>Cα<br>Cα<br>Π<br>Π<br>1ο<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V | CC*<br>to 70<br>Dindition<br>Linputs<br>Linputs<br>                                                            | VCC= 1<br>IS<br>DC<br>DC<br>GND<br>GND<br>I <sub>0</sub> = 0mA<br>C | olts<br>C<br>5V±5<br>0.<br>2.(<br>0.<br>3.<br>-1<br>-1 | n<br>00<br>7<br>0<br>0<br>0 | Max<br>0.8<br>0.45<br>10<br>10<br>10                | Unit<br>V<br>V<br>V<br>μΑ<br>μΑ<br>mA       |

| Symbol<br>V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>OH</sub><br>V <sub>OL</sub><br><sup>1</sup> IN<br><sup>1</sup> OZ<br><sup>1</sup> DD1<br><sup>1</sup> OS | Pro<br>Op<br>*Exc<br>erating<br>HIGH lev<br>LOW leve<br>HIGH lev<br>LOW leve<br>Input leak<br>3-state o<br>VCC sup<br>Output st        | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>ameter<br>rel input<br>el output<br>el output (Note 1)<br>el output (Note 1)<br>cage<br>utput leakage<br>oply (standby)                           | VPF<br><sup>T</sup> A<br>rammin | 2 V<br>0<br>1g<br>Cα<br>Cα<br>Π<br>Π<br>1ο<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V | CC*<br>to 70<br>Dindition<br>Linputs<br>Linputs<br>- 4mA<br>- 4mA<br>/CC or 0<br>VCC or<br>or GND,<br>/0 = VC0 | VCC= 1<br>IS<br>DC<br>DC<br>GND<br>GND<br>I <sub>0</sub> = 0mA<br>C | olts<br>C<br>5V±5<br>0.<br>0.<br>3.<br>-1<br>-1<br>-1  | n<br>00<br>7<br>0<br>0<br>0 | Max<br>0.8<br>0.45<br>10<br>10<br>10<br>140         | Unit<br>V<br>V<br>V<br>µA<br>µA<br>mA<br>mA |

| Symbol<br>V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>OH</sub><br>V <sub>OL</sub><br><sup>1</sup> IN<br><sup>1</sup> OZ<br><sup>1</sup> DD1<br><sup>1</sup> OS | Pro<br>Op<br>*Exc<br>erating<br>Par<br>HIGH lev<br>LOW leve<br>HIGH lev<br>LOW leve<br>Input leak<br>3-state o<br>VCC sup<br>Output si | ogram Voltage<br>erating Ambient<br>cept during prog<br>Characteristic<br>rameter<br>rel input<br>el output (Note 1)<br>el output (Note 1)<br>el output (Note 1)<br>cage<br>utput leakage<br>oply (standby)<br>hort circuit | VPF<br><sup>T</sup> A<br>rammin | > V<br>0<br>1g<br>Cc<br>TT<br>10<br>V<br>-V<br>-V<br>V<br>-V<br>V<br>-V<br>V                                | CC*<br>to 70<br>Dindition<br>Linputs<br>Linputs<br>- 4mA<br>- 4mA<br>/CC or 0<br>VCC or<br>or GND,<br>/0 = VC0 | VCC= 1<br>IS<br>DC<br>DC<br>GND<br>GND<br>I <sub>0</sub> = 0mA<br>C | olts<br>C<br>5V±5<br>0.<br>0.<br>3.<br>-1<br>-1<br>-1  | n<br>00<br>7<br>0<br>0<br>0 | Max<br>0.8<br>0.45<br>10<br>10<br>10<br>140<br>-100 | Unit<br>V<br>V<br>V<br>µA<br>µA<br>mA<br>mA |

2. Sample tested 3. Includes worst case 84LCC package pin capacitance.

# AC Characteristics Commercial Temperature & Voltage ( $VCC=5V \pm 5\%$ TA $0^{\circ} + 70^{\circ}$ ) $V_{IL}=OV; V_{IH}=3; V; V_{OL}=V_{OH}=1.5V$

| Macro Description                               | Fanout                       |      | 1    |            | 2    |      | 3    |      | 4    |      | 8    |  |

|-------------------------------------------------|------------------------------|------|------|------------|------|------|------|------|------|------|------|--|

|                                                 |                              | MIN  | MAX  | <u>MIN</u> | MAX  | MIN  | MAX  | MIN  | MAX  | MIN  | MAX  |  |

| Gates Using 1 Module                            | <sup>t</sup> PD <sub>1</sub> | 6.1  | 9.3  | 6.8        | 9.9  | 7.6  | 11.4 | 8.4  | 12.8 | 11.2 | 16.0 |  |

| Gates Using 2 Modules                           | <sup>t</sup> PD <sub>2</sub> | 10.1 | 16.0 | 10.8       | 16.6 | 11.6 | 18.1 | 12.4 | 19.5 | 15.2 | 22.7 |  |

| Latches                                         | <sup>t</sup> PD              | 6.1  | 9.3  | 6.8        | 9.9  | 7.6  | 11.4 | 8.4  | 12.8 | 11.2 | 16.0 |  |

|                                                 | <sup>t</sup> su              | 4.1  | 5    | 4.5        | 5.5  | 4.9  | 6    | 5.3  | 6.5  | 5.7  | 7    |  |

|                                                 | t <sub>H</sub>               | 4.1  | 5    | 4.9        | 6    | 5.7  | 7    | 6.5  | 8    | 7.3  | 9    |  |

| Flip-flops                                      | <sup>t</sup> PD              | 6.1  | 9.3  | 6.8        | 9.9  | 7.6  | 11.4 | 8.4  | 12.8 | 11.2 | 16.0 |  |

| Note: T <sub>SU</sub> is independent of fanout. | <sup>t</sup> su              | 4.1  | 5    | 4.1        | 5    | 4.1  | 5    | 4.1  | 5    | 4.1  | 5    |  |

|                                                 | tH                           | 0.0  | 0.0  | 0.0        | 0.0  | 0.0  | 0.0  | 0.0  | 0.0  | 0.0  | 0.0  |  |

| Input Buffer                                    | <sup>t</sup> PLH             | 7.8  | 8.9  | 8.1        | 9.6  | 9.4  | 11.2 | 10.2 | 12.1 | 14.6 | 17.3 |  |

|                                                 | <sup>t</sup> PHL             | 8.6  | 10.2 | 9.4        | 11.1 | 10.8 | 12.8 | 11.9 | 14.1 | 16.7 | 19.8 |  |

|              |                 | MIN | МАХ |

|--------------|-----------------|-----|-----|

| Clock Buffer | <sup>t</sup> LH | 11  | 15  |

|              | tHL             | 12  | 16  |

|                |                  | 50 PF |     | NS   | /PF  |

|----------------|------------------|-------|-----|------|------|

|                |                  | MIN   | MAX | MIN  | МАХ  |

| Output Buffers | <sup>t</sup> PLH | 5.6   | 6.9 | 0.04 | 0.06 |

|                | <sup>t</sup> PHL | 7.0   | 8.6 | 0.04 | 0.06 |

|                                         |   |                  | MIN | MAX | MIN  | MAX  |

|-----------------------------------------|---|------------------|-----|-----|------|------|

| Output Buffers, TS<br>and Bidirectional |   | <sup>t</sup> PLH | 5.6 | 6.9 | 0.04 | 0.06 |

|                                         | D | <sup>t</sup> PHL | 7.0 | 8.6 | 0.04 | 0.06 |

|                                         | _ | t PZH<br>t PHZ   | 5.2 | 6.9 |      |      |

|                                         | E | t PZL<br>t PLZ   | 7.0 | 8.6 |      |      |

Note:

1. All T<sub>PD</sub> include interconnect delays.

2. All delays include statistical estimates for wiring delay; actual delay values are determined after place and route.

# Determining ACT1 Dyanmic Power Calculations

The following is the formula for calculating typical dynamic chip power consumption in milliwatts.

Total Chip Power = 0.15N\*F1 + 0.012M\*F2 + 2.6P\*F3

Where:

F1 = Average logic module switching rate in MHz

F2 = Average clock pin switching rate in MHz

F3 = Average I/O switching rate in MHz

M = No. of logic modules connected to clock pin

N = Number of logic modules used on the chip

P = Number of I/O pairs used (input + output), with 50 pF load.

Note:

The power is calculated for a typical interconnect and a fanout of 3 from each of the logic modules.

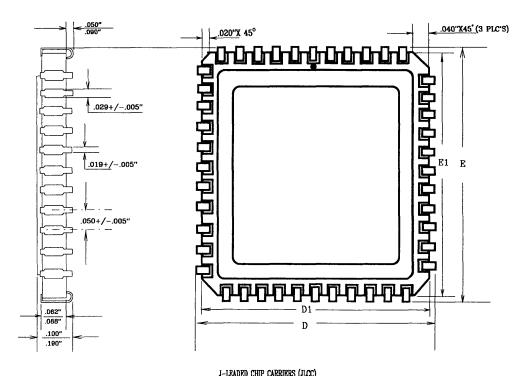

# Package Dimensions

| 9-19990 ED | ыш | CHIMININ | (114.0) |  |

|------------|----|----------|---------|--|

|            |    |          |         |  |

|            | FORM WID | TH (D, E) | BODY WIDTH (D1, E1) |           |  |  |

|------------|----------|-----------|---------------------|-----------|--|--|

| lead count | NOMINAL  | TOLERANCE | NOMINAL             | TOLERANCE |  |  |

| 44         | .690"    | .010"     | .650"               | .010"     |  |  |

| 68         | .990"    | .010"     | .950"               | .010"     |  |  |

| 84         | 1.190"   | .010"     | 1.150"              | .010"     |  |  |

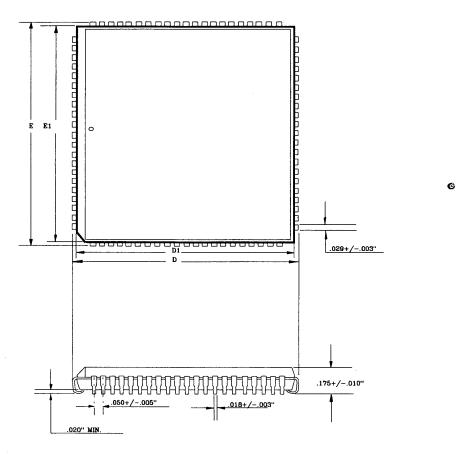

# Package Dimensions

| LEAD COUNT | D, E          | E1, D1      |

|------------|---------------|-------------|

| 44         | 690+/005"     | .655+/005"  |

| 68         | 990+/005"     | .955+/005"  |

| 84         | 1.190+/~.005" | 1.155+/005" |

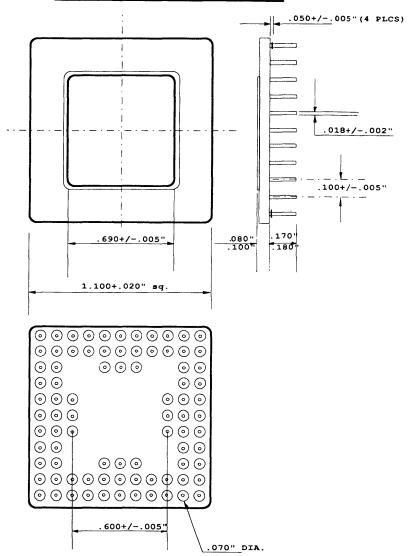

# **Package Dimensions**

**84 PIN PGA OUTLINE DRAWING**

# ACT 1 Desktop Configurable Gate Arrays

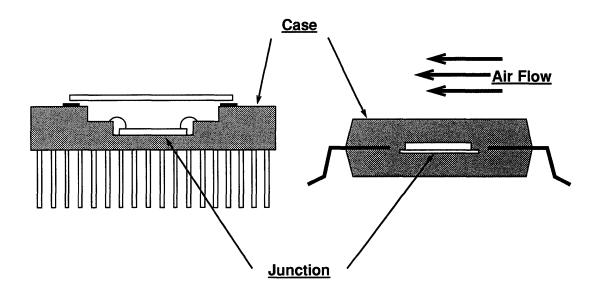

| ACT 12XXX Package | Thermal Resist | ance |                          |                       |

|-------------------|----------------|------|--------------------------|-----------------------|

| Package Type      | Pin Count      | Øjc  | ⊘ja <sup>still</sup> air | <u>∅ja</u> 300 ft/min |

| Ceramic PGA       |                | 8    |                          | 20                    |

| Plastic LCC       |                | 15   |                          | 40                    |

|                   | 68             | 13   | 45                       | 35                    |

|                   | 84             | 12   | 44                       | 33                    |

| Ceramic JLCC      | 44             | 5    |                          |                       |

|                   | 68             | 5    |                          | 25                    |

|                   | 84             | 7    |                          |                       |

$\emptyset$ jc =  $\emptyset$ ja =  $\Delta$ T $\emptyset$ ja

# Notes on package pin designations:

- 1. All pins marked GND are I/O ground connections and must be connected to circuit ground.

- 2.. All pins marked GNDA are internal array grounds and must be connected to circuit ground.

- 3. V<sub>PP</sub> must be terminated to VCC except during programming.

- 4. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- 5. MODE must be terminated to circuit ground except during programming\*.

- 6. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os\*.

- 7. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. They will be driven low by the device.

- 8. All unidentified pins on the package outline drawings are standard I/Os.

- \* Note:

The security fuse must be programmed for SDI and DCLK to function as I/Os.

For device debugging on the user's circuit board, MODE, SDI and DCLK should be terminated to circuit ground through  $a \ge 10$ K ohm resistor. They can be tied to ground if not debugging.

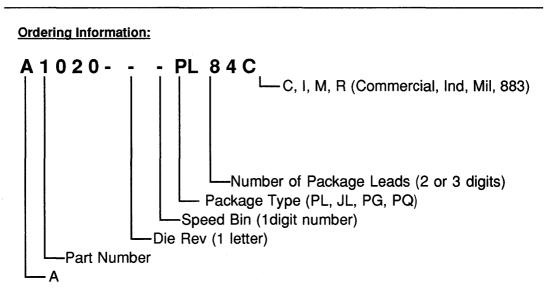

Unused parts are left out when identifying a product.

## **Actel Macro Library**

The ACT1010/1020 is supported by a macro library of over 150 standard logic functions. These range from simple logic gates to complex functions such as counters, decoders and comparators. All Library components are hard macros with fixed characteristics uness otherwise specified. The Actel logic module implements logic functions with inverted inputs as efficiently as non-inverted inputs, without an increase in propagation delay. By taking advantage of the various combinations of input polarity, the use of separate inverters can be virtually eliminated.

# **Action Logic System**

# **Actel Macro Library**

**Action Logic System**

# **Action Logic System**

# **Actel Macro Library**

# **Actel Macro Library**

O

## **Actel Soft Macros**

# Macro Name Description

# Module Count

# **TTL Equivalents:**

| T1383 to 8 decoder w/active low enable, inv out | 11 |

|-------------------------------------------------|----|

| T1392 to 4 decoder w/enable, inv out            | 4  |

| T1518 to 1 MUX w/ enable, true and inv out      | 5  |

| T1534 to 1 MUX w/ active low enable             | 2  |

| T1572 to 1 MUX w/enable                         | 1  |

| T161A4 bit counter                              |    |

| T1648 bit parallel out serial shift register    |    |

| T1814 bit alu                                   |    |

| T1944 bit shift register                        | 14 |

| T1954 bit shift register                        |    |

| T273octal D ff w/clear                          |    |

| T2698 bit up/down counter                       |    |

| T280parity generator/checker                    |    |

| T377octal D ff w/active low enable              |    |

# **Decoders:**

| DEC2X4   | .2 to 4 decoder                    | 4  |

|----------|------------------------------------|----|

| DEC2X4A  | .2 to 4 decoder, inv out           | 4  |

| DECE2X4  | .2 to 4 decoder w/enable           | 4  |

| DECE2X4A | .2 to 4 decoder w/enable, inv out  | 4  |

| DEC3X8   | .3 to 8 decoder w/enable           | 8  |

| DEC3X8A  | .3 to 8 decoder w/ enable, inv out | 9  |

| DECE3X8  | .3 to 8 decoder w/enable           | 11 |

| DECE3X8A | .3 to 8 decoder w/enable, inv out  | 11 |

| DEC4X16A | .4 to 16 decoder, inv out          | 20 |

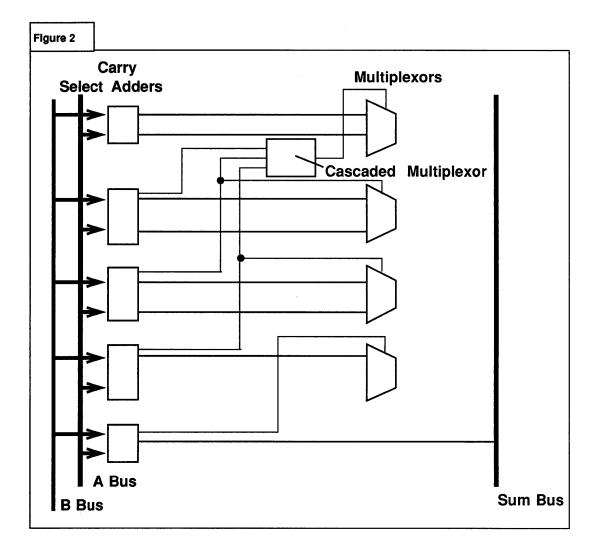

# Fast Adders:

| FADD8  | 8 bit fast adder  |     |

|--------|-------------------|-----|

| FADD12 | 12 bit fast adder | 58  |

| FADD16 | 16 bit fast adder |     |

| FADD24 | 24 bit fast adder | 120 |

| FADD32 | 32 bit fast adder | 160 |

# **Multiplexers:**

| MX88 to 1 MUX           | 3 |

|-------------------------|---|

| MX8A8 to 1 MUX, inv out | 3 |

| MX16 16 to 1 MUX        |   |

## Actel Soft Macros, cont.

| Macro Name              | Description                                                                                                                                  | Module Count |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                         | . octal register w/ preset & clear<br>. octal register, inv, clock, enable, preset, & clear                                                  |              |

| Identity Compara        | itors:                                                                                                                                       |              |

| СМР8                    | . 4 bit identity comparator<br>. 8 bit identity comparator<br>. 16 bit magnitude comparator                                                  | 9            |

| Magnitude Comp          | arators                                                                                                                                      |              |

| MCMP2<br>MCMP4<br>MCMP8 | . 2 bit Mag comparator w/ enables<br>. 4 bit Mag comparator w/ enables<br>. 8 bit Mag comparator w/ enables<br>. 16 bit magnitude comparator | 18<br>36     |

| Latches:                |                                                                                                                                              |              |

| LATM8                   | . octal latch w/enable<br>. octal latch, MUXed inputs<br>. octal latch w/clear                                                               | 8            |

| Shift Registers:        |                                                                                                                                              |              |

| SREG4                   | . 4 bit shift register w/clear<br>. 8 bit shift register w/clear                                                                             |              |

| Counters:               |                                                                                                                                              |              |

|                         | . 4 bit binary ctr. (active high-carry out) w/ clear, pre-<br>. 4 bit loadable binary counter                                                |              |

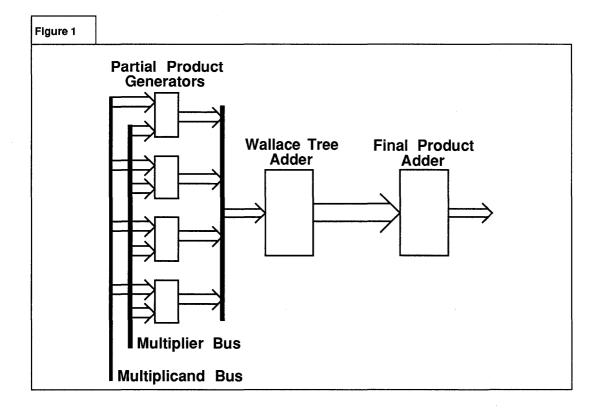

| Multiplier:             | (active low-carry out) w/clear, preset)                                                                                                      | 10           |

|                         | . 8 X 8 twos complement multiplier                                                                                                           | 235          |

| IIL-to-Acter    | Cross Reference Guide                 |

|-----------------|---------------------------------------|

| TTL Part Number | Actel Libary Component Name           |

| 7400            | NAND2                                 |

| 7402            | NOR2                                  |

| 7404            | INV                                   |

| 7408            | AND2                                  |

| 7410            | NAND3                                 |

| 7411            | AND3                                  |

| 7420            | NAND4                                 |

| 7421            | AND4                                  |

| 7427            | NOR3                                  |

| 7432            | OR2                                   |

| 7474            | DFPC (PRE active high)                |

| 7486            | ХО                                    |

| 74109           | JKFPC (PRE active high)               |

| 74138           | T138                                  |

| 74139           | T139                                  |

| 74151           | T151                                  |

| 74153           | T153                                  |

| 74157           | T157                                  |

| 74161A          | T161A                                 |

| 74164           | T165                                  |

| 74181           | T181                                  |

| 74183           | FA1B (Carry-in, Carry-out active low) |

| 74191           | T191                                  |

| 74194           | T194                                  |

| 74273           | T273                                  |

| 74269           | T269                                  |

| 74280           | T280                                  |

| 74377           | Т377                                  |

| 74810           | XNOR                                  |

|                 |                                       |

# TTL-to-Actel Cross Reference Guide

# **Application Notes:**

Gate Array Design UART Design

# **Applications Briefs:**

Three-Stating ACT 1010/1020 Designs ALU181 Fast Adders 8-bit Twos Complement Multiplier The Actel Timer Using the Actionprobes Metastability

## Introduction

#### About the Actel Application Guide for ACT 1 Gate Arrays

This Application Guide explains how to design circuits for Actel logic devices while obtaining maximum efficiency of logic module utilization and maximum performance. It also describes both desirable and undesirable (i.e., error-producing) design practices.

The first sections focus on use of the Actel macro library for efficient logic module utilization.

Next the guide describes design practices which affect both utilization efficiency and performance.

The Guide then describes the use of MUXs to implement circuits which would otherwise use three-state functions.

Finally, the Guide covers performance and routability for Actel Gate Array designs with special focus on critical paths and I/O pin assignment.

ACT, Action Logic, Activator, Actionprobe and PLICE are trademarks of Actel Corporation. Viewlogic is a registered trademark of Viewlogic Systems, Incorporated.

## **Most Efficient Actel Macros**

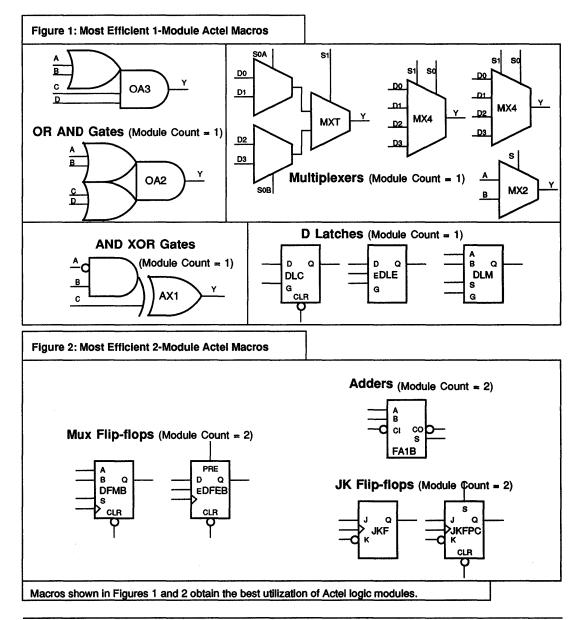

Certain classes of Actel macros allow a maximum amount of logic function to be implemented using a minimal number of Actel logic modules.

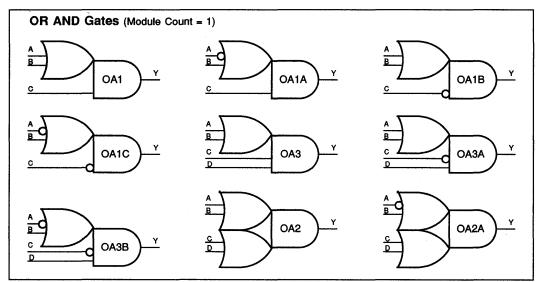

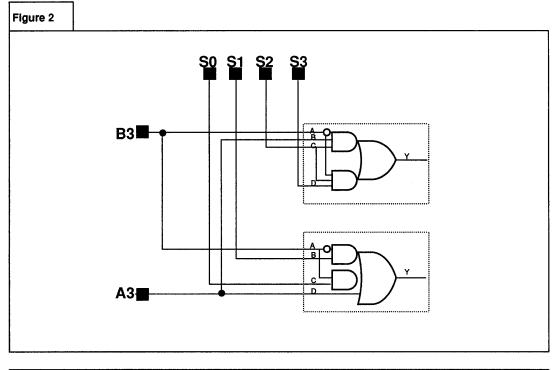

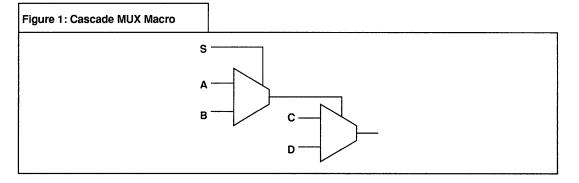

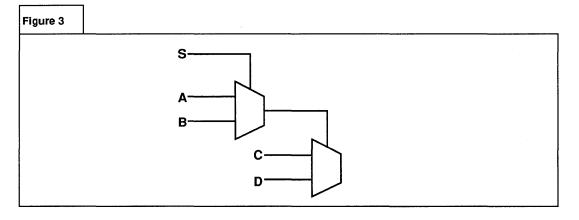

Figure 1 below shows the most efficient one-module Actel macros; Figure 2 shows the most efficient two-module Actel Macros.

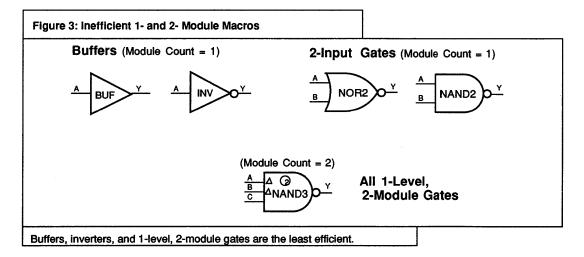

## The Least Efficient Actel Macros

#### **Buffers and Inverters**

Buffers and inverters are the least efficient Actel macros. Designers should avoid using them except where necessary to reduce fanout. Eliminate inverters by using gates with input negation bubbles. (See the section in this guide about negation bubbles.)

Buffers are necessary to reduce fanouts to acceptable numbers, although buffers can sometimes be eliminated by using redundant logic functions.

### Two-Input Gates

Two-input gates are also relatively inefficient. To avoid using two-input gates, use instead MUX inputs on flip-flops, where possible, to implement two-input functions.

### 1-level, 2-Module Gates

Single level logic gates requiring two Actel modules are inefficient and add extra delay on some pins; avoid using these gates when possible.

# Gate Array Design

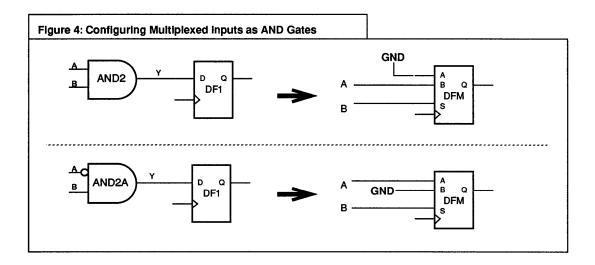

# Configuring Multiplexed Inputs as AND Gates

Sometimes a simple logic function preceding a flip-flop or latch can be eliminated by incorporating the function into a flipflop or latch having MUX input capability. See Figure 4 Below.

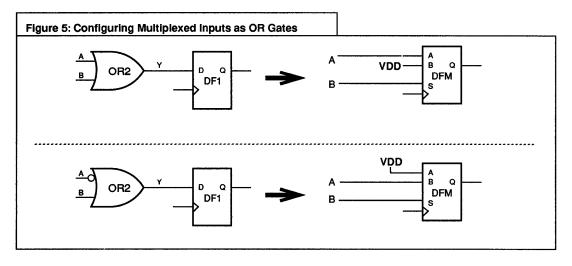

# Configuring Multiplexed Inputs as OR Gates

Using MUX inputs on flip-flops and latches can help eliminate simple logic functions which would otherwise require an additional logic module. In this way, it is possible to fit more logic functionality into an ACT device. See Figure 5 below.

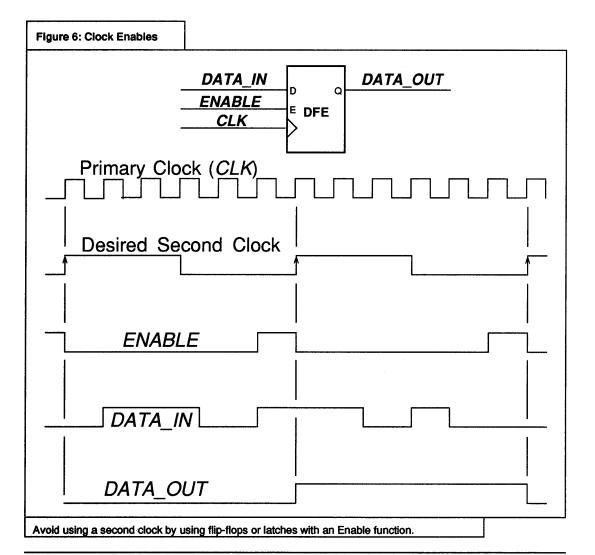

## **Clock Enables**

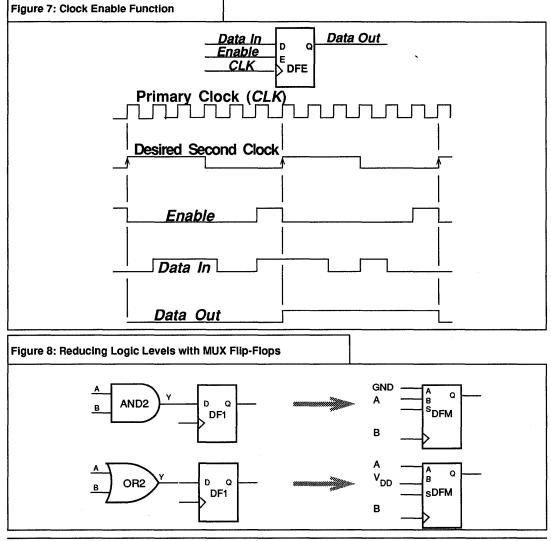

Clock Enables allow data storage and transfer at different intervals while using a common clock

Common clock, synchronous systems work best. These systems are the easiest to design, debug, and analyze for timing constraints. When it is necessary to store data at a time interval differing considerably from the primary clock frequency, it may seem desirable to introduce a second clock. Usually, however, the designer may avoid this second clock by using flip-flops or latches with an Enable function. See Figure 6 below.

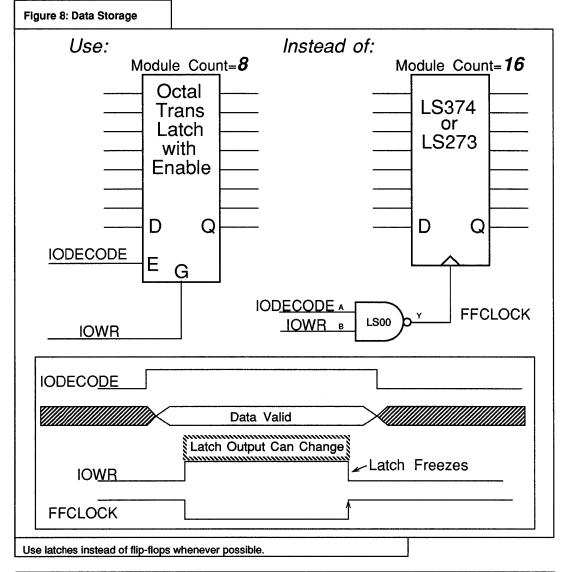

## **Efficient Data Storage**

Where possible, use transparent latches instead of D flip-flops for data storage, because they use only one logic module (flip-flops use two logic modules).

For example, with a data register in a typical microprocessor system, if a simple data storage function is possible using a transparent latch *or* a flip-flop, use the <u>latch</u> instead. See Figure 8 below.

Since data storage may require many elements, the additive advantage of using latches instead of flip-flops is often significant in the overall completed design.

# **Application Note**

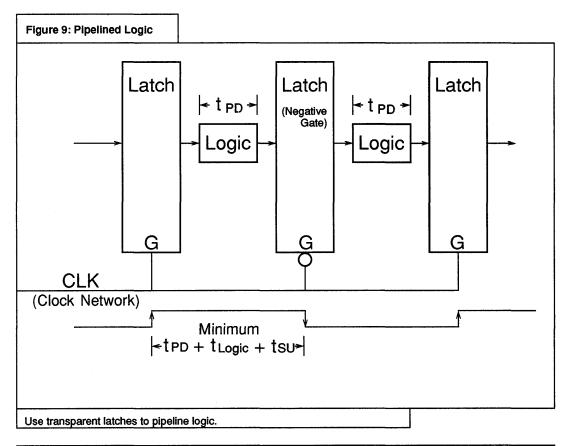

#### Pipelined Logic Using Transparent Latches

In addition to transferring pipelined data, transparent latches may also be used for pipelined logic where the timing considerations are as shown in Figure 9.

To facilitate pipelined applications using transparent latches, the Actel macro library includes both negative and positive gates on latch macros; this facilitates the use of the clock's opposite phases.

This design practice has the same effect as a two-phase clock system, yet uses only the single clock network found in ACT devices.

# **Gate Array Design**

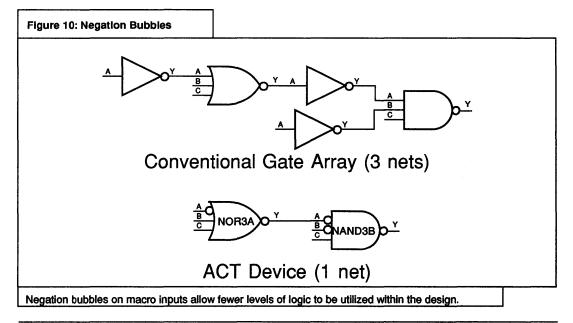

## Negation Bubbles

TTL-based system designs generally have numerous inverters (usually LS04s) throughout the design. Most designs implemented in conventional gate arrays also extensively use inverters.

In contrast to TTL-based systems and conventional gate-arrays, designs implemented on ACT devices use fewer inverter macros due to a unique feature of the Actel macro library: negation bubbles on macro inputs.

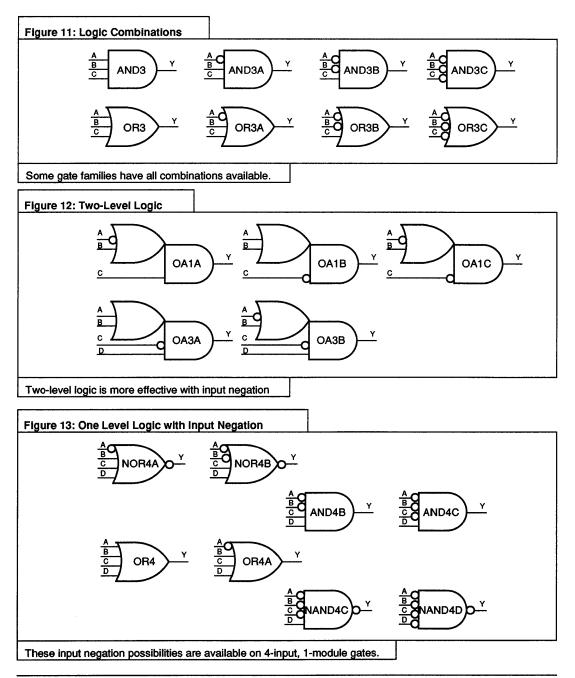

In addition to gate structures found in most gate array libraries, the Actel macro library includes structures with inversion bubbles, in different combinations, on logic module inputs. Taking advantage of these macros helps minimize the number of logic modules required to implement your logic function. Figures 11, 12 and 13 on the next page show how input negation makes logic more effective. Potentially more important is the *INCREASE IN PERFORMANCE* made possible using fewer logic module and wiring delays in paths. Figure 15 below compares an ACT design and a gate array implementing the same function.

In this example, the conventional gate array has four macro delays, while the ACT design has only two delays.

Figures 16-18 on page 15 show how different families of Actel macros contain different combinations of input negation bubbles.

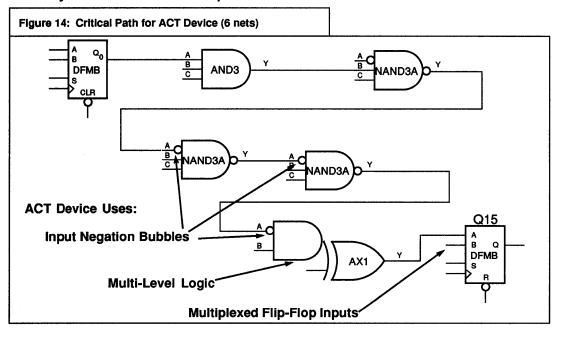

Figures 14 and 15 on page 11 show a critical path from a 16-bit synchronous counter example, implemented both in a conventional gate array, and in Actel macros. Note that the ACT design requires only six nets in the path, compared to 11 nets for the gate array.

## **Negation Bubbles on Macro Inputs**

# ACT Device vs. Conventional Gate Array: 16-Bit Synchronous Counter Comparison

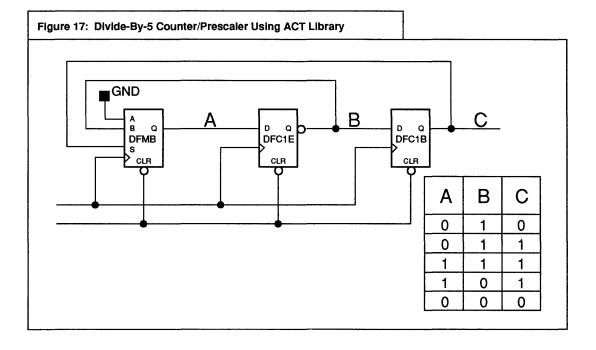

## High-Speed Prescalers/Counters

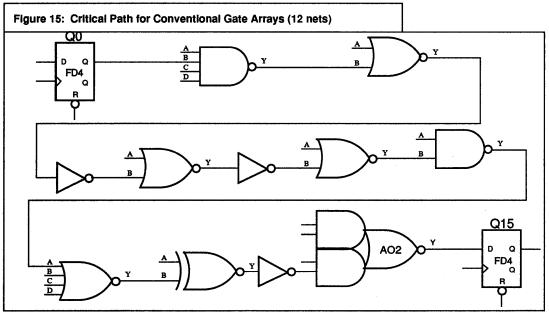

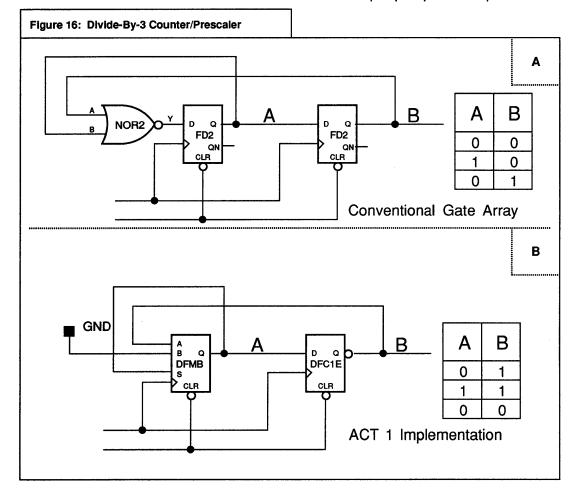

It is often necessary to pre-scale an incoming signal or create a pattern of waveforms, using a very high speed synchronous counter. This is possible in the ACT 1 architecture using the logic functions of input MUXs on certain flip-flop macros.

Figure 16 below shows a Divide-By-3 counter (also called a modulo 3 counter) implemented in two ways. Part A of Figure 16 shows a conventional masked-programmed gate array requiring a separate

NOR gate, in addition to the two flip-flop macros. Part B of Figure 16 shows effective use of the ACT library: the modified NOR function fits one AND configuration, made possible by the MUX input. The second flip-flop now has an inverting output suited to the gate function of the MUX input on the first flip-flop.

The state table for the counter has changed, but it still implements a divideby-3 function without additional delay between flip-flop outputs and inputs.

Similar principles were applied in creating the divide-by-5 counter/prescaler shown below in Figure 17. When using circuits like these to create a widely-used, lower frequency clock, it may be necessary to attach a prescaler output to the ACT clock network dedicated I/O pin. If this is true, be careful to place the prescaler input and output I/O pins close to the dedicated clock pin. Also, watch the delays on the net which drives the prescaler clock; it will be more prone to clock skew than the dedicated clock network.

# **Application Note**

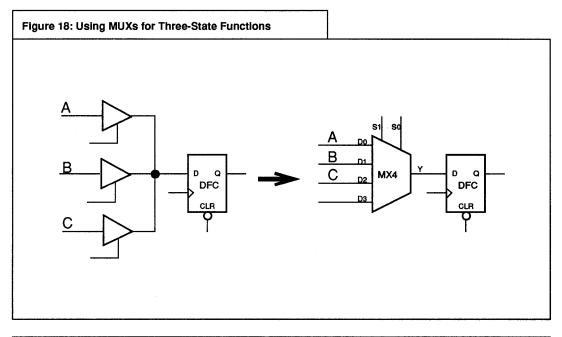

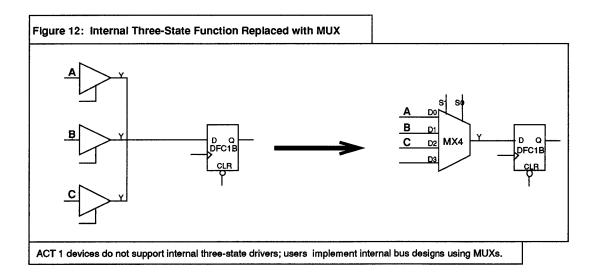

#### Use MUXs Instead of Three-State Buffers in ACT devices

ACT devices do not have true three-state functionality for circuits implemented within the device. However, it is easy to implement all three-state functions using MUXs. See Figure 18 below.

Since MUX-type structures are the most efficient of all Actel macros, using MUXs produces an added performance benefit (MUXs are always faster than three-state alternatives). Using MUXs also removes the problem of bus conflicts.

Use MUX inputs on flip-flops, when possible, to gain an efficiency and performance advantage.

# **Gate Array Design**

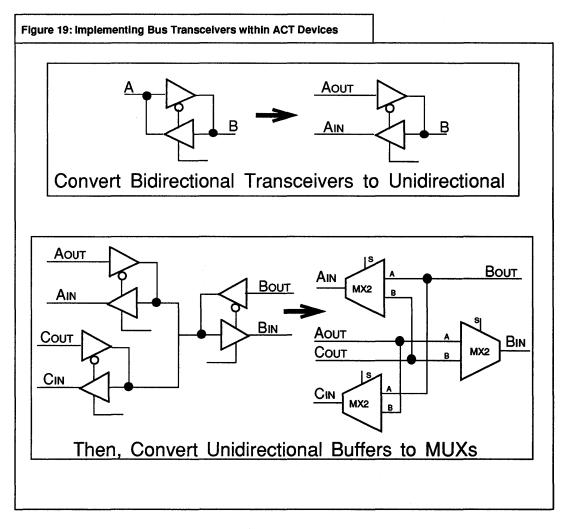

### Internal Three-state Transceiver Functions

When implementing internal three-state transceiver functions in ACT devices connecting multiple bus structures, the process is easier if performed in two steps as shown in Figure 19. First break bi-directional structures into two unidirectional structures. It is then simple to complete conversion to a MUX-based circuit.

### Designing for Performance and Routability

Modification of *tanout* and *I/O assignment* may significantly improve the performance and routability of your design. Fanout considerations are addressed below and on the next page; I/O assignment is discussed on page GA-18.

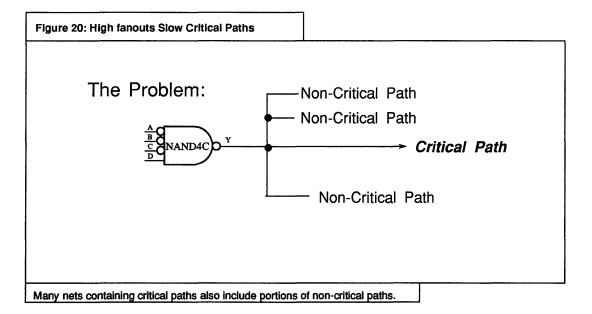

#### Designing Fanout for Optimized Performance and Routability

Consider a net in one of the design's critical paths, illustrated in Figure 20 below.

Of all input pins on the net, only the input pin in the critical path is important to optimizing the design's performance. The other input pins on the net create additional loading, slowing signals propagating along the critical path.

Excessive fanouts also create longer, more complex nets, causing routing congestion and limiting the design's routability. This reduces the ACT device's logic capacity for the desired application.

To solve this problem, isolate the critical path from the non-critical paths, as shown on page 19, without disturbing the logical function of the circuit.

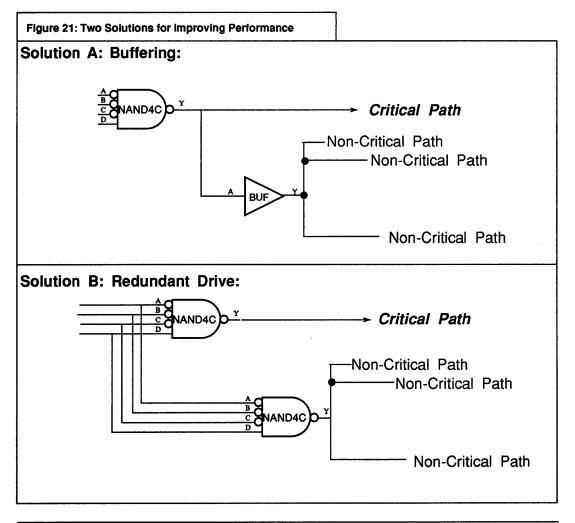

There are two solutions to the problem of high fanout on a critical path. Solution A buffers the non-critical paths to reduce fanout on the critical path.

When the added buffer delay is too detrimental to the non-critical paths, Solution B (redundant logic) is an alternative. Solution B requires that the added loading on input nets does not cause additional timing problems.

Another way to improve critical net performance is to label the net "critical" causing the Route program to optimize the routing of the net. However, to achieve the greatest performance improvements, both careful isolation of critical paths and careful choice of I/O pin assignment are necessary.

Assigning I/O Pins For Optimized Performance and Routability

When the Placement program assigns module locations to implement Actel hard macros, it evaluates the I/O pin locations to optimize I/O placement.

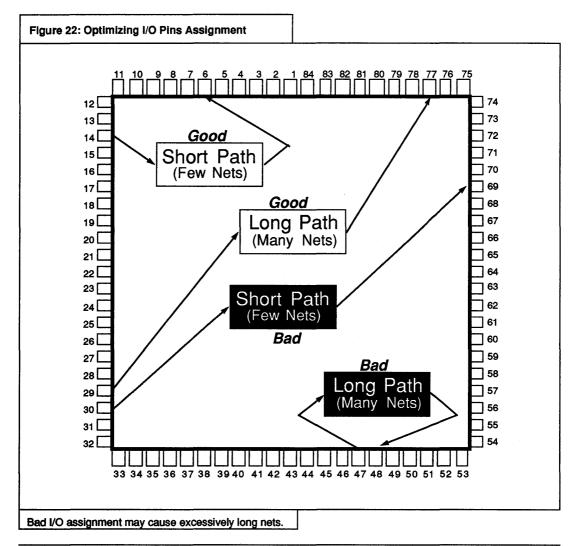

Figure 22 shows poor I/O pin assignment may cause excessively long nets if the I/Os of a short logic path are too far apart. For long logic paths, (i.e., paths containing many levels of logic), poorly placed I/O pins may also cause long nets if they are too close together.

Long nets add routing congestion, limiting the design's capacity, and adding additional delay.

For optimum design performance, pay careful attention to I/O pin assignment. For example, if I/Os are "scattered" around the package periphery, a design with low module utilization will likely have long nets with excessive delays.

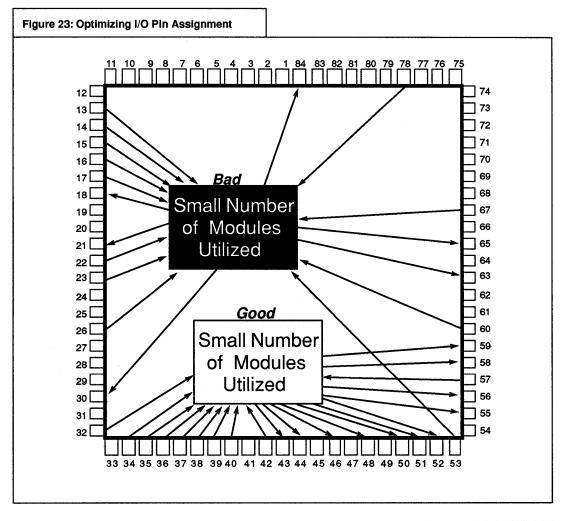

When assigning I/O pins for designs utilizing a relatively small percentage (<50%) of the available logic modules, it is preferable to assign I/O pins so that they are relatively close together. See Figure 23, below.

### About the Actel Application Note for UART Design

This Application Note demonstrates the design of a complex circuit using Actel desktop configurable gate arrays. The Note will show:

- 1. the flexibility of ACT 1 family architecture;

- features of the ACT 1 macro library which speed and simplify the design process;

- the Actel design process using Viewlogic design entry and the Action Logic<sup>™</sup> System;

- 4. how to design a Universal Asynchronous Receiver & Transmitter (UART) with the Actel Design Process.

ACT, Action Logic, Activator, Actionprobe and PLICE are trademarks of Actel Corporation. Viewlogic is a registered trademark of Viewlogic Systems, Incorporated.

## **UART Description**

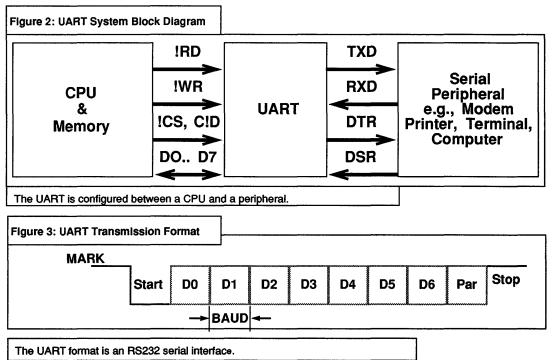

The UART is a serial communication device which handles transmission and reception of information between computers and peripherals including modems, terminals and printers. This Note describes a general purpose UART which utilizes 178 logic modules in the ACT 1010, representing approximately 700 gates.

Figure 2 below shows the UART configured as a controller between a computer and a peripheral device. Communications protocol is a standard RS232 serial interface.

The UART transmission format is shown in Figure 3 below. A start bit begins the transmission, followed by the data bits, and then an optional even or odd parity bit. A programmed number of stop bits concludes the transmission.

## UART Design

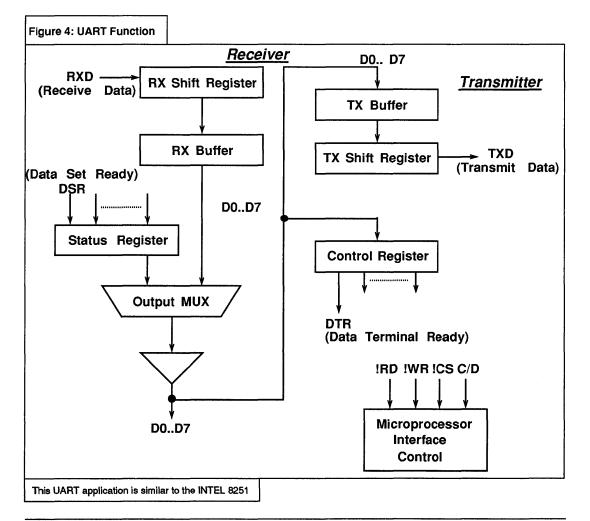

The UART application described in this Note is similar to the INTEL 8251 operating asynchronously. See Figure 4 below.

When the CPU sends a data character, the UART automatically adds a start bit, followed by 7 (or 8) data bits, an even or odd parity bit, and a stop bit. The UART then transmits this "packet" as a serial data stream on the TXD output. It shifts out serial data a rate equal to 1/16 the clock frequency (pin 16XBAUDCLK). When the CPU receives a data character, a falling edge on the UART's RXD input triggers the beginning of a start bit. The start bit is again checked to prevent a false start. If the start bit is valid, the data character is shifted in, followed by one stop bit. A serial stream of data is then converted to parallel format, ready for CPU retrieval.

# **UART Design**

## **Transmitter Design**

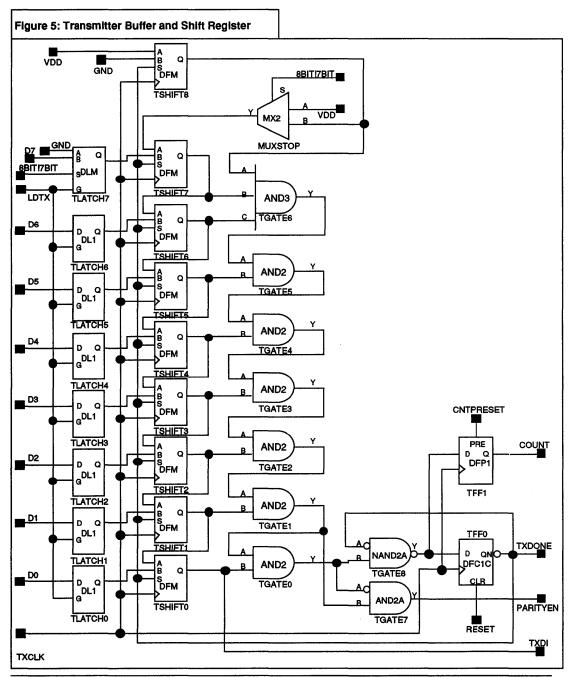

Figure 5 below shows the transmitter's buffer and shift register.

# **Application Note**

The transmitter first latches the parallel data word D[0:7] from the CPU in the buffer TLATCH[0:7]. It then transfers the data character to the shift register TSHIFT[0:7] through the B inputs. After the first clock (TXCLK), TXDONE goes low selecting the A inputs of TSHIFT[0:7]. TXCLK then serially shifts out the data character. A series of AND gates (TGATE0-TGATE6) detect a logic high, indicating the stop bit, propagating through the shift register.

## Transmitter Buffer

The transmitter buffer TLATCH[0-7] uses transparent latches to store a data charac-

ter. The level-sensitive transparent latch consumes only one ACT 1 logic module.

Because of the wide variety of latches available in the ACT 1 library, designers may build efficient registers for any application: synchronous clear, gate-enable, active high or low outputs, and active high or low gates.

## Clocks

It is also possible to construct a twophase clock system by combining active high gate latches and active low gate latches. See Figure 6 below.

# **UART Design**

The ACT 1 macro library includes a large selection of edge-sensitive storage elements (flip-flops, or FF's). FFs are available with asynchronous clear, asynchronous preset and clock enable inputs. Negation bubbles are available on all inputs and outputs.

The clock enable feature allows separation of data storage and transfer while maintaining a common clock system. See Figure 7, below.

## Transmitter Shift Register

The transmitter's shift register TSHIFT[0:7] uses flip-flops with a built-in 2:1 multiplexor (MUX) on the D input. The built-in MUX can emulate 2-input logic functions as shown in Figure 8 below.

The MUX flip-flop uses two logic modules (as does a standard flip-flop). It is thus possible to construct a parallel load/serial shift register without additional logic.

# **Application Note**

# **UART Design**

#### **Transmitter Clock Circuit**

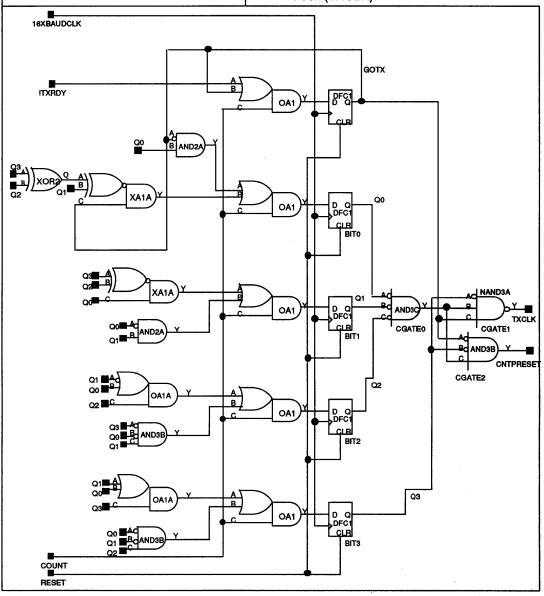

Figure 9: Transmitter Clock Circuit

The clock circuit is shown below in Figure 9. It is implemented as a 4-bit Gray code counter with both synchronous and asynchronous reset (COUNT & RESET, respectively) and count enable (GOTX). An external clock signal (16XBAUDCLK) drives the state machine. Two AND gates CGATE0 & CGATE1 decode the outputs Q3-Q0 of the state machine and generate an internal clock (TXCLK) for the transmitter shift register. Only one bit changes at a time, eliminating glitches on the transmitter clock (TXCLK).

# **Application Note**

## **UART Design**

#### TWO-Level Logic

The transmitter state machine takes advantage of the OR/AND macro, a twolevel logic function using only one logic module. In combinatorial logic, use of twolevel logic functions can significantly reduce the module count. There are different types of OR/AND macros with a wide choice of input combinations. Refer to the ACT 1 family data sheet for a list of OR/AND and AND/OR macros.

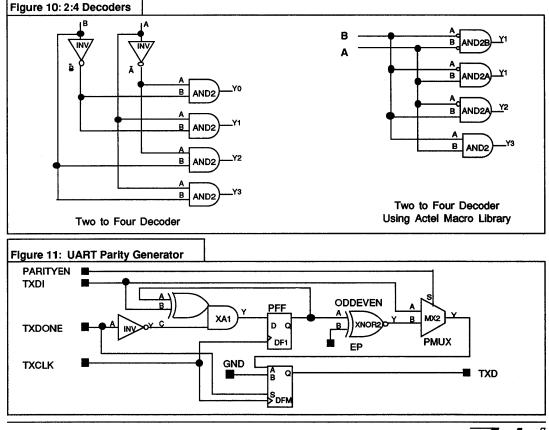

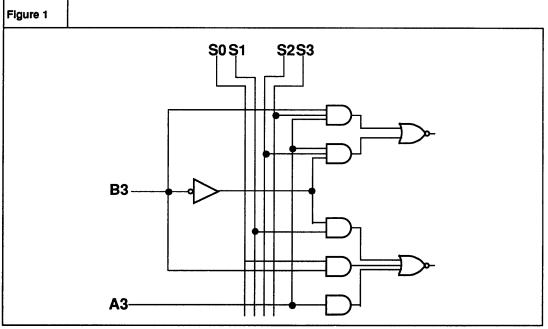

#### Decoders

Decoder functions require signals and their complements. Using negation assertion levels available on Actel macros simplifies the logic path and conserves module usage. See the 2:4 decoder in Figure 10, below. It is important to note that propagation delay through a logic module is independent of the implemented function. Thus the designer should use negation bubbles and two level logic macros whenever possible.

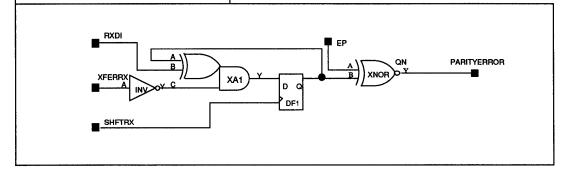

#### **Parity Generation**

The transmitter parity generator is programmable for odd or even parity. See Figure 11 below.

From the shift register, data serially enters the parity generator on the transmit line (TXDI). The generator inserts the parity bit just prior to the stop bit. A 2:1 MUX (PMUX) selects either data or parity bit to the data transmit line TXD.

## Logic Module Conservation

Efficient utilization of Actel macros allows implementation of the UART transmitter section using only 75 of the 295 available logic modules on the ACT 1010 array. The parity generator uses the XOR/AND macro. The XOR/AND, XOR/OR, and AND/XOR functions utilize only one logic module.

ACT 1 devices are also particularly efficient at implementing MUX functions. Both 2:1 and 4:1 MUXs can each be implemented in only one logic module. Since ACT 1 devices do not support internal three state drivers, MUXs implement internal bus designs. See Figure 12 below.

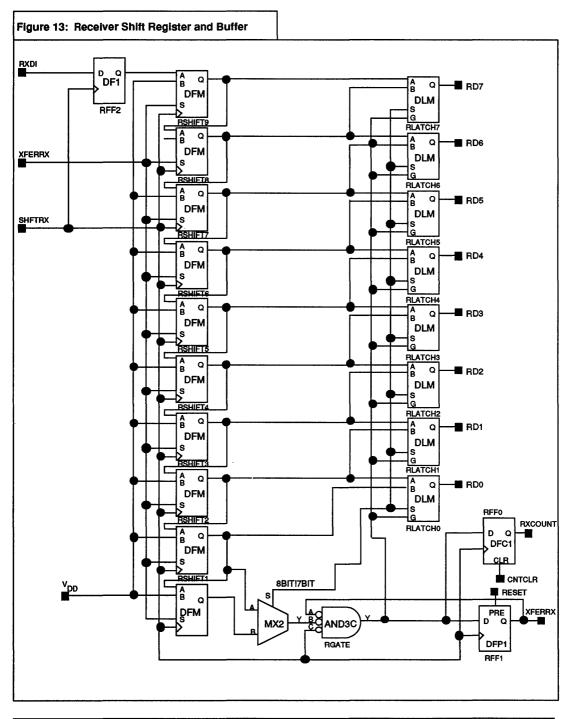

## **Receiver Design**

### Shift Register and Buffer

Figure 13 on the next page shows the schematic of the receiver's shift register and buffer. A logical "1" is loaded into

the receiver shift register RSHIFT[0:9]. After the first clock (SHFTRX), XFERRX goes low, selecting the A inputs of the MUX flip-flops. The low start bit precedes the serial data shifts into the register. When a complete serial data character shifts into the register, the parallel data character transfers to the buffer (0:7) for CPU access.

The receiver design takes advantage of the single-module transparent latch with MUX, minimizing required circuitry. Similarly, the built-in MUX can emulate other two-variable functions.

The MUX can also emulate an inverter, effecting a negation at the data input of the transparent latch.

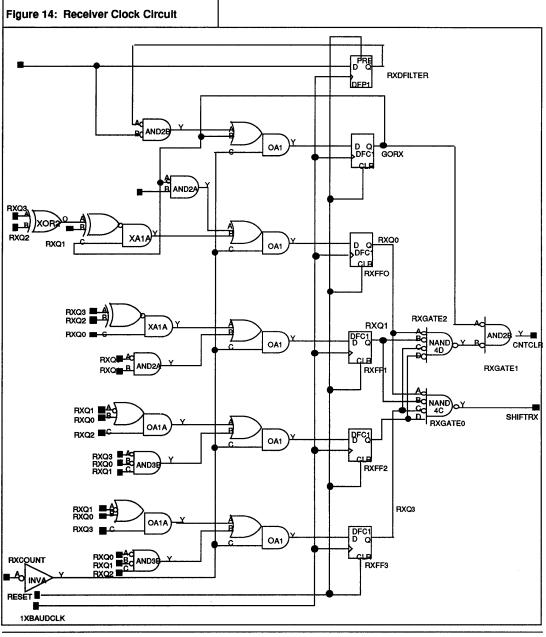

## **Receiver Clock Circuit**

The receiver clock circuit is a 4-bit Gray code counter (similar to the transmitter clock circuit) and is driven by the same external clock signal (16BAUDCLK).

# **Application Note**

# **UART Design**

The state machine has both synchronous and asynchronous resets (RXCOUNT, RESET). A filter circuit (RXDFILTER) prevents false starts due to errors on the data line (RXDI). The receiver clock (SHFTRX) is decoded from the outputs of the state machine RXQ[0:3].

# **UART** Design

## **Parity Checker**

The receiver parity checker is programmable to either odd or even parity.

The parity checker generates a parity bit from the incoming serial data stream and compares it to the incoming parity bit. The

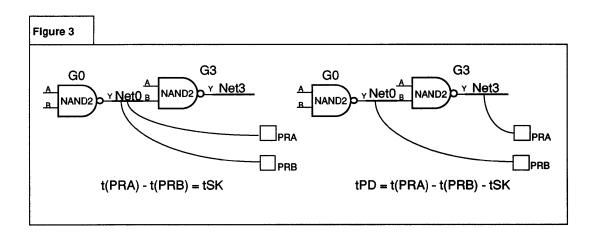

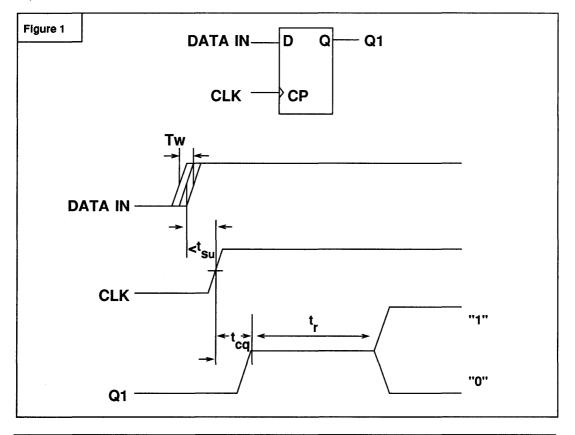

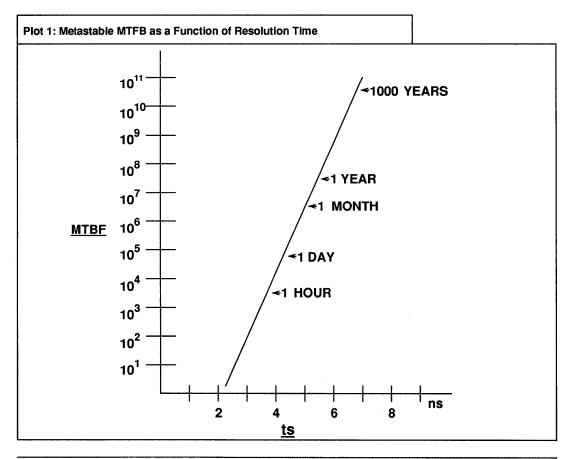

Figure 15: Parity Error Generator